エンジニア向けボードレベルカメラの統合に関するヒント

基板レベルのカメラ統合に適したインタフェースの選定

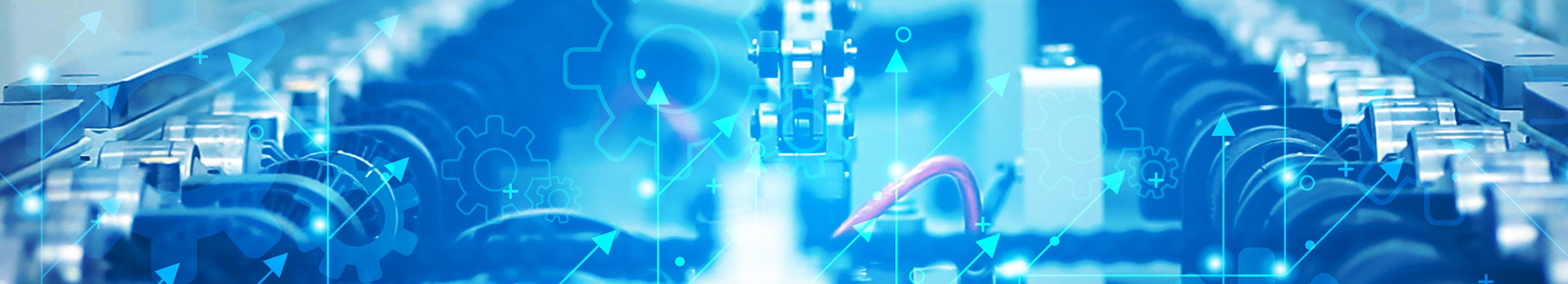

USB 3.1、MIPI CSI-2、LVDS:帯域幅、遅延、リアルタイム同期におけるトレードオフ

組み込みエンジニアは、基板レベルのカメラ統合におけるインタフェース選択に際して、極めて重要なトレードオフに直面します。USB 3.1 は高帯域幅(5 Gbps)を提供するため、HD 動画ストリーミングに適していますが、そのプロトコルオーバーヘッドにより 5~10 ms の遅延が発生し、リアルタイム制御ループへの適用性が制限されます。MIPI CSI-2 はスケーラブルな帯域幅(レーンあたり最大 6 Gbps)およびハードウェアトリガーによる同期機能を備えており、サブミリ秒級の遅延と高精度なマルチセンサタイミングを実現します。これは産業用自動化およびロボティクスに最適です。LVDS はシンプルな直列プロトコルを用いて、決定論的かつ超低遅延(<1 ms)の伝送を提供しますが、チャネルあたりの帯域幅は約 655 Mbps に制限されており、低解像度または圧縮済みストリームへの使用に限定されます。カメラ間の厳密な同期を要するビジョンシステムでは、MIPI CSI-2 を優先すべきです。自律走行車の知覚など、安全性が極めて重要なアプリケーションでは、LVDS のタイミング予測可能性が有益です。USB 3.1 は、コスト重視・非リアルタイムの HD 監視用途において、わずかな遅延が許容される場合に依然として有効です。ただし、熱的および処理能力に関する制約については事前に検証が必要です。

インタフェースによる信号整合性およびPCBレイアウトのベストプラクティス

信号整合性はインタフェース固有のものであり、信頼性の高い基板レベルカメラ性能を実現するための基盤となる要素です。USB 3.1では、90Ωの差動インピーダンスを維持し、長さをマッチさせたペア(±5ミル)、グラウンドシールドされた配線、およびノイズの多いデジタルトレースからの厳密な分離を実施して、EMIを抑制する必要があります。MIPI CSI-2では、各差動レーンごとに100Ωのインピーダンスを確保し、長さのマッチングを±10ミル以内に収め、特に1.5 Gbpsを超える高速レーンにおいては、受信器近傍へのビア配置を回避しなければなりません。LVDSレイアウトでは、トレース長を短く(10インチ未満)保ち、一貫した100Ωのインピーダンスを維持するとともに、クロストークを抑制するためのガードトレースを配置する必要があります。すべてのインタフェースにおいては、アナログセンサ回路とデジタルISPおよびプロセッサ領域とを分離するためにグラウンドプレーンを分割し、デカップリングコンデンサを電源ピンから2 mm以内に配置し、連続したリファレンスプレーンを備えた4層以上(4+層)のスタックアップを採用してください。不適切な配線は、試作段階のビジョンシステムにおける画像アーティファクトの原因の32%を占めており、ミッションクリティカルな設計においては、配線後のシミュレーションおよびインピーダンス検証が必須となります。

機械的統合:レンズマウントと光学的柔軟性

精密なレンズ取り付けが不可欠です。ミクロンスケールの位置ずれは、フォーカスのドリフト、歪み、または解像度の低下を引き起こします。エンジニアは、衝撃・振動耐性に不可欠な機械的剛性と、現場での調整性(通常はねじ式バレルまたはシム式マウントによって実現)とのバランスを取る必要があります。光学的柔軟性には、固定焦点レンズ、可変焦点レンズ、液体レンズなど、さまざまなレンズタイプへの互換性に加え、ヘリカル機構やモータ制御装置を用いた焦点距離のチューニング対応が求められます。レンズとセンサー間の熱膨張係数(CTE)の不一致は、緩和措置(例:インバー、セラミック複合材などの低CTE材料の使用、または運動学的マウント)を講じる必要があります。これは特に産業環境(−40°C~+85°C)において重要です。赤外線またはマルチスペクトル撮像では、基板材料のターゲット波長帯域における透過性(例:LWIRではゲルマニウム、UVでは溶融シリカ)が、最優先の設計要件となります。モジュラー式レンズインターフェースにより、完全な再キャリブレーションを伴わずに迅速なレンズ交換が可能になりますが、フレンジ距離の公差は vignetting(周辺減光)やMTF(モジュレーション転送関数)の劣化を防ぐため、10 µm以下に保つ必要があります。

基板レベルのカメラ設計における堅牢なシステムレベル共存の確保

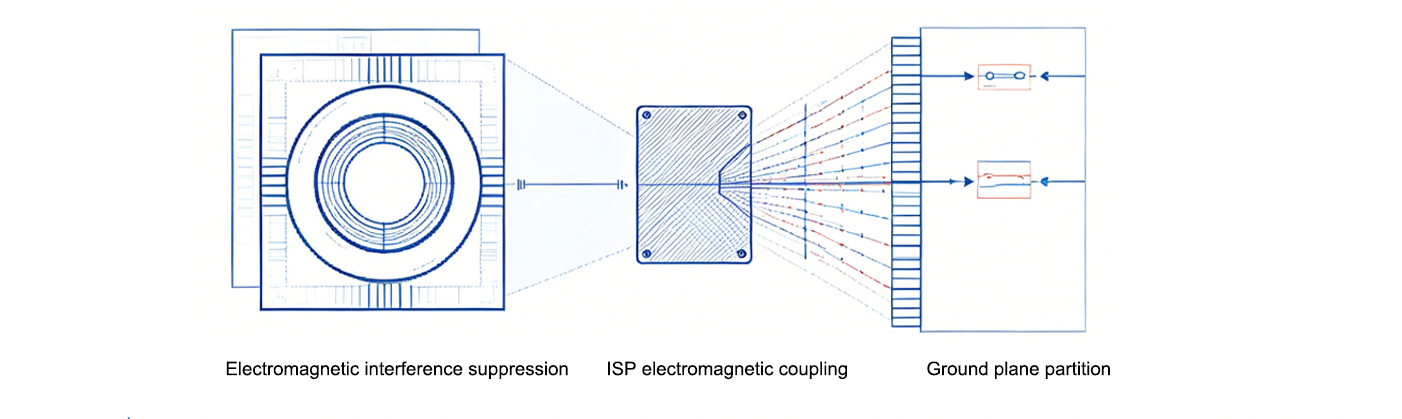

センサ―ISP共存のためのEMI低減およびグラウンドプレーン分割

筐体が付いていない基板レベルのカメラ設計では、密閉型モジュールに備わるEMIシールドが欠けており、イメージセンサとISP(Image Signal Processor)間のPCBレベルにおける分離がより重要となる。アナログセンサ領域とデジタルISPサブシステムを分離するための分割グランドプレーンは、伝導性ノイズ結合を最小限に抑えるために不可欠である。なぜなら、ミックスドシグナル干渉によって50 dBμV/mを超えるクロック高調波(IEC 61000-4-3)が発生する可能性があるからである。有効な対策には、電源入力部におけるスター接地点方式のグランディング、高速デジタル信号線の周囲にステッチングビア付きガードトレースを配置すること、センサ近傍のグランドパワーポアにサーマルリリーフを設けないこと、およびI²Cクロックラインにフェライトビーズを追加することが挙げられる。センサとISP間の距離が最高動作周波数における3λを下回ると、信号完全性は急激に劣化するため、インピーダンス制御配線および長さマッチングされた差動ペア配線が必須となる。近接場EMIプローブ(5 mm間隔)を用いた早期プロトタイピングにより、ホットスポットを特定できる。また、センサ上に局所的にミューメタルシールドを施すことで、放射エミッションを12–18 dB低減できる(FCC OET-65)。ミックスドシグナル領域間のクリアランスを≥40 mil以上に保つことで、高解像度モジュールにおけるSNR(信号対雑音比)が一貫して20%向上する。

ボードレベルカメラ向けソフトウェア統合およびSDKの移植性

クロスプラットフォームドライバーサポート:Linux RT、QNX、およびベアメタルRTOS(Spinnaker対応)

クロスプラットフォームソフトウェアの移植性は、Linuxリアルタイム(RT)、QNX、およびリソースが制限されたベアメタルRTOS環境にまたがる組込みビジョン展開において不可欠です。各OSは、タイミング、メモリ、ドライバーモデルに関する固有の要件を課しますが、画素単位で正確な画像取得およびハードウェアトリガーによる同期は、一貫して維持されなければなりません。統一されたSDK抽象化層がこのギャップを埋めます。例えばSpinnaker SDKは、x86、ARM、RISC-Vプラットフォーム間で標準化されたAPIを提供するとともに、リアルタイムフレームキャプチャ、ハードウェアトリガリング、ISPレジスタアクセスをネイティブにサポートします。これにより、Linux RT産業用PCからマイコンベースのRTOSターゲットへの移行時に、重複するドライバー開発が不要になります。このようなフレームワークを活用するチームでは、統合期間を最大40%短縮できる一方で、熱的デレーティングや電圧スケーリングといった条件下でも、決定論的な動作を維持できます。

OEM量産向けの基板レベルカメラ統合を効率化する準備はできましたか?

シームレス 基板レベルカメラ統合 信頼性が高く、高性能な組込みビジョンシステムの根幹を成すのは、インターフェース選択の不適切さ、信号整合性の欠陥、あるいは最適化されていない機械的設計を、いかなる高度なアルゴリズムや処理ハードウェアでも補うことはできません。現場で実証済みの統合ベストプラクティスに従い、事前に検証済みのハードウェア、リファレンスデザイン支援、およびクロスプラットフォームソフトウェアツールを提供するカメラベンダーと連携することで、設計の反復回数を削減し、市場投入までの期間を短縮するとともに、量産OEM製品において一貫性とコスト効率の両立した性能を実現できます。

産業用レベルの基板レベルカメラソリューションを、お客様の組込みビジョンアプリケーションに合わせてカスタマイズする場合、または完全なリファレンス設計パッケージ、社内エンジニアリングサポート、およびHIFLYが提供するカスタムOEM製造サービスへのアクセスをご希望の場合には、産業用マシンビジョン分野における専門知識を有するベンダーと提携してください。HIFLYは、基板レベルカメラ設計、フルOEM/ODMカスタマイズ、エンドツーエンドの組込みビジョンシステム統合に至るまで、15年にわたる実績を誇ります。ISO 9001:2015認証を取得し、グローバルな規制対応支援および専任のデザインインエンジニアリングサービスも提供しています。本日すぐにお問い合わせください。無償のコンサルテーション、カスタムプロトタイピング、あるいは基板レベルカメラ統合ワークフローの最適化についてご相談いただけます。